مع التطور السريع للذكاء الاصطناعي، أصبحت خوادم الذكاء الاصطناعي ومجموعات وحدات معالجة الرسومات هي البنية التحتية الأساسية للحوسبة في مراكز البيانات. بدءاً من تدريب النماذج اللغوية الكبيرة إلى خدمات الاستدلال في الوقت الحقيقي، تفرض هذه التطبيقات متطلبات غير مسبوقة على أداء الحوسبة وإنتاجية البيانات. في البنية الأساسية التي تدعم هذه الأنظمة عالية الأداء، تواجه تكنولوجيا نقل الإشارات عالية السرعة تحديات شديدة في البنية الأساسية التي تدعم هذه الأنظمة عالية الأداء.

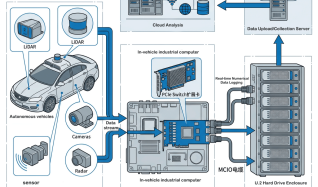

وفقًا لمؤسسات أبحاث الصناعة، تجاوز سوق وحدات معالجة الرسومات العالمي 40 مليار دولار في عام 2024، بمعدل نمو سنوي يزيد عن 30%. يمكن لخادم تدريب ذكاء اصطناعي واحد أن يدمج 8 أو أكثر من وحدات معالجة الرسومات عالية الأداء، مما يشكل مجموعة حوسبة موحدة من خلال الربط البيني عالي السرعة. تفرض بنية الحوسبة عالية الكثافة هذه متطلبات عالية للغاية على عرض النطاق الترددي لنقل البيانات وجودة الإشارة داخل الخادم.

وفي الوقت نفسه، تخضع أنظمة التخزين أيضًا لعملية تحول. لم يعد التخزين التقليدي SATA و SAS قادرًا على تلبية احتياجات أعباء عمل الذكاء الاصطناعي، وأصبحت محركات أقراص الحالة الصلبة عالية السرعة القائمة على بروتوكول NVMe هي السائدة. الجيل الجديد CXL (رابط الحوسبة السريع) تعمل التقنية على رفع مستوى توسيع الذاكرة وتقارب التخزين، مما يسمح لوحدات معالجة الرسومات ووحدات المعالجة المركزية بالوصول إلى موارد الذاكرة والتخزين عن بُعد بطريقة مترابطة مع ذاكرة التخزين المؤقت.

بصفته المعيار السائد للتوصيل البيني للأجهزة الداخلية في الخوادم، فقد تطور PCI Express (PCIe) إلى الجيل الخامس ووصل إلى مرحلة النضج. يزيد PCIe 5.0 من معدل الإرسال لكل مسار من 16GT/s (PCIe 4.0) إلى 32 جيجابت/ثانيةمما يضاعف عرض النطاق الترددي لكل مسار. بالنسبة لبطاقات الرسومات أو محولات الشبكة بتكوين x16، يمكن أن يصل عرض النطاق الترددي النظري ثنائي الاتجاه إلى 128 جيجابايت/ثانية.

ومع ذلك، فإن معدلات الإرسال الأعلى تقدم أيضاً تحديات هندسية جديدة:

· توهين الإشارة: تعاني الإشارات عالية السرعة من فقدان عند إرسالها من خلال آثار وموصلات ثنائي الفينيل متعدد الكلور؛ ويزداد التوهين سوءاً عند الترددات الأعلى. تتمتع إشارات PCIe 5.0 بمسافة نقل فعالة أقصر من PCIe 4.0، مما يتطلب تصميم توجيه أكثر صرامة.

· تكامل الإشارة: تكون الإشارات عالية السرعة أكثر عرضة للحديث المتبادل والانعكاس والضوضاء، مما قد يتسبب في حدوث أخطاء في نقل البيانات وتدهور استقرار النظام.

· هامش التوقيت: معدلات البيانات الأعلى تعني نوافذ توقيت أضيق، مما يفرض متطلبات أكثر صرامة على مزامنة الساعة ودقة حافة الإشارة.

لمعالجة تحديات نقل الإشارات عالية السرعة, ريتيمر ظهرت التكنولوجيا. جهاز ريتيمر هو جهاز لتجديد الإشارات يوضع في مسار الإشارة عالية السرعة، يكتشف الإشارات المخففة ويستعيدها ويعيد ضبطها لتوسيع مسافة الإرسال الفعالة وتحسين سلامة الإشارة.

على عكس مضخمات الإشارات البسيطة (Redrivers)، تحقق أجهزة إعادة الإشارات تجديد الإشارة من خلال الآليات التالية:

· معادلة الإشارة: يعوض عن التوهين عالي التردد ويستعيد سعة الإشارة.

· استرداد الساعة والبيانات (CDR): يستخرج الساعة من إشارة الدخل لإزالة الارتعاش.

· إعادة توقيت الإشارة: يعيد توليد إشارات بيانات نظيفة باستخدام الساعة المستردة.

· شفافية البروتوكول: لا يقوم بتحليل محتوى البيانات وهو شفاف تمامًا لبروتوكولات الطبقة العليا.

في خوادم الذكاء الاصطناعي وأنظمة التخزين المتطورة، أصبحت رقاقات Retimer مكونات حاسمة تضمن نقل إشارات عالية السرعة يمكن الاعتماد عليها. فهي تلعب دورًا لا غنى عنه في التوصيل البيني بين وحدات معالجة الرسومات ووحدات المعالجة المركزية، وكذلك في التوصيلات الموسعة لمحركات أقراص NVMe SSD.

CXL (وصلة الحوسبة السريعة) هو بروتوكول ربط بيني جديد عالي السرعة يعتمد على الطبقة المادية PCIe 5.0 ولكن بوظائف أكثر ثراءً. يدعم بروتوكول CXL 2.0 القياسي ثلاثة بروتوكولات:

· CXL.io: متوافق مع بروتوكولات PCIe لاكتشاف الجهاز وتكوينه.

· ذاكرة التخزين المؤقت CXL.cache: يدعم ترابط ذاكرة التخزين المؤقت للجهاز، مما يسمح للأجهزة بمشاركة ذاكرة التخزين المؤقت لوحدة المعالجة المركزية.

· CXL.memory: يدعم الوصول الدلالي للذاكرة، مما يتيح للأجهزة الوصول المباشر إلى ذاكرة النظام.

تكمن القيمة الأساسية لتقنية CXL في كسر عنق زجاجة ذاكرة وحدة المعالجة المركزية في البنى التقليدية، مما يسمح للمسرعات مثل وحدات معالجة الرسومات و FPGAs بالوصول إلى مجموعات الذاكرة ذات السعة الكبيرة بطريقة متماسكة مع ذاكرة التخزين المؤقت. وهذا أمر بالغ الأهمية لتدريب الذكاء الاصطناعي وتطبيقات البيانات الضخمة التي تتطلب ذاكرة ضخمة.

MCIO (Mini Cool Edge IOOO) هو معيار موصل مدمج عالي السرعة مصمم للجيل القادم من تطبيقات PCIe وCXL. يوفر MCIO المزايا التالية:

· كثافة أعلى: يدعم المزيد من قنوات الإشارة في مساحة أصغر.

· تكامل إشارة أفضل: يقلل التصميم المحسّن للدبابيس وتصميم التدريع من التداخل.

· توصيل الكابلات: يدعم توصيل الأجهزة الخارجية عبر الكابلات، مما يكسر قيود مساحة الهيكل.

يتطلب تدريب نماذج الذكاء الاصطناعي الكبيرة تعاون مئات أو حتى آلاف وحدات معالجة الرسومات. يضمن الربط البيني عالي السرعة تبادل بيانات التدرج ومعلمات النموذج بين وحدات معالجة الرسومات في زمن انتقال منخفض ونطاق ترددي عالٍ بين وحدات معالجة الرسومات. تضمن تقنية Retimer سلامة الإشارة عبر اللوحات الخلفية المعقدة وكابلات المسافات الطويلة.

تتطلب تطبيقات الحوسبة عالية الأداء مثل الحوسبة العلمية والمحاكاة والتسلسل الجيني متطلبات عالية للغاية لعرض النطاق الترددي للذاكرة وسعتها. يمكن أن يؤدي توسيع ذاكرة CXL مع تحسين إشارة Retimer إلى إنشاء مجمعات ذاكرة ذات سعة كبيرة وعرض نطاق ترددي عالٍ لتسريع مهام الحوسبة.

تعمل خوادم الألعاب السحابية على محاكاة افتراضية لمثيلات متعددة لوحدة معالجة الرسومات على جهاز فعلي واحد لتوفير خدمات العرض في الوقت الفعلي لمختلف المستخدمين. يعد التخزين عالي السرعة والوصول إلى الذاكرة أمرًا بالغ الأهمية لضمان توفير تجارب ألعاب منخفضة التأخير.

تحتاج حلول التخزين المعرّف بالبرمجيات (SDS) القائمة على الخوادم القياسية إلى توصيل عدد كبير من محركات أقراص الحالة الصلبة NVMe SSD. تتيح بطاقات التوسعة PCIe 5.0 Retimer 5.0 توسيع محركات أقراص الحالة الصلبة عالية الكثافة لإنشاء مجمعات تخزين عالية الأداء.

في مواجهة متطلبات الربط البيني عالي السرعة المتزايدة التعقيد، يجب على مصممي الأنظمة مراعاة العوامل التالية:

· مسافة الإرسال: قم بتقييم المسافة المادية التي يجب أن تقطعها الإشارات لتحديد ما إذا كانت هناك حاجة إلى تعزيز ريتيمير.

· تكوين المسار: حدد أوضاع تشعب PCIe المناسبة (x16/x8/x4) بناءً على متطلبات الجهاز.

· دعم البروتوكول: تأكيد ما إذا كانت هناك حاجة إلى دعم بروتوكول CXL والمتطلبات الوظيفية المحددة لـ CXL.

· التصميم الحراري: تتميز رقائق ريتيمر عالية السرعة باستهلاك طاقة عالية نسبيًا وتتطلب حلولاً حرارية مناسبة.

· التحقق من التوافق: تأكد من توافق بطاقة التوسعة مع اللوحات الأم وأنظمة التشغيل والأجهزة المستهدفة.

يعمل ظهور عصر الذكاء الاصطناعي على إعادة تشكيل تصميم بنية مركز البيانات. بدءًا من الإرسال عالي السرعة في PCIe 5.0، وتجديد الإشارات في تقنية ريتيمر، إلى توسيع الذاكرة في بروتوكول CXL، تدعم كل تقنية إطلاق إمكانات حوسبة الذكاء الاصطناعي.

بالنسبة للمؤسسات التي تخطط للبنية التحتية للذكاء الاصطناعي، فإن فهم مبادئ وسيناريوهات تطبيق هذه التقنيات الأساسية يساعد على إجراء اختيارات تقنية أكثر عقلانية وبناء منصات حوسبة عالية الأداء والموثوقية.

شركة Linkreal (LR-LINK) هي شركة وطنية ذات تقنية عالية تركز على حلول توصيل الخادم/مركز البيانات. وتشمل مجموعة منتجاتها محولات شبكة الإيثرنت، وبطاقات توسيع التخزين، وحلول توسيع وحدة معالجة الرسومات، وما إلى ذلك. ومواكبةً لاتجاهات تطوير تقنيات PCIe 5.0 وCXL، توفر الشركة حلول توسيع الإشارة عالية السرعة لخوادم الذكاء الاصطناعي والحوسبة عالية الأداء والتخزين المعرّف بالبرمجيات وسيناريوهات التطبيقات الأخرى.